### **General Description**

The MAX14840E/MAX14841E are +3.3V ESD-protected transceivers intended for half-duplex RS-485 communication up to 40Mbps. These transceivers are optimized for high speeds over extended cable runs while minimizing tolerance to noise.

The MAX14840E features symmetrical fail-safe and larger receiver hysteresis, providing improved noise rejection and improved recovered signals in high-speed and long cable applications. The MAX14841E has true failsafe receiver inputs guaranteeing a logic-high receiver output when inputs are shorted or open.

The MAX14840E/MAX14841E transceivers draw 1.5mA (typ) supply current when unloaded or when fully loaded with the drivers disabled. Hot-swap capability eliminates undesired transitions on the bus during power-up or hot insertion.

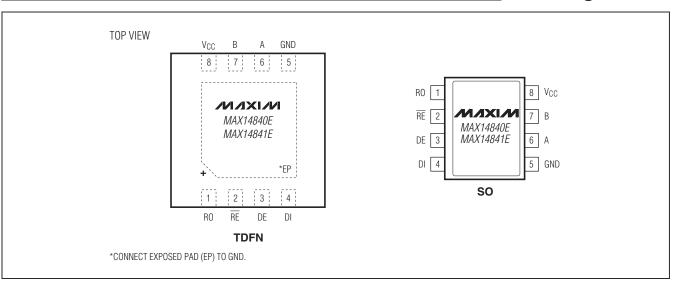

The MAX14840E/MAX14841E are available in 8-pin SO and small, 8-pin (3mm x 3mm) TDFN-EP packages. Both devices operate over the -40°C to +125°C automotive temperature range.

### **Applications**

Motion Controllers Fieldbus Networks Industrial Control Systems Backplane Buses **HVAC Networks**

### **Features**

- ♦ Half-Duplex RS-485 Transceivers

- ♦ +3.3V Supply Voltage

- ♦ 40Mbps Maximum Data Rate

- ◆ Large (170mV) Receiver Hysteresis on MAX14840E

- ♦ Symmetrical Fail-Safe Receiver Input on MAX14840E

- ◆ Fail-Safe Receiver Input (MAX14841E)

- ♦ Hot-Swap Capability

- Short-Circuit Protected Outputs

- ♦ Thermal Self-Protection

- ♦ Low 10µA (max) Shutdown Current

- ♦ Extended ESD Protection for RS-485 I/O Pins ±35kV Human Body Model (HBM) ±20kV Air-Gap Discharge per IEC 61000-4-2 ±12kV Contact Discharge per IEC 61000-4-2

- ♦ Automotive -40°C to +125°C Operating **Temperature Range**

- ♦ Available in Industry-Standard 8-Pin SO or Space-Saving, 8-Pin TDFN-EP (3mm x 3mm) **Packages**

### **Ordering Information/Selector Guide**

| PART          | FAIL SAFE                                       | TEMP RANGE      | PIN-PACKAGE |

|---------------|-------------------------------------------------|-----------------|-------------|

| MAX14840EASA+ | <b>X14840</b> EASA+ Symmetrical -40°C to +125°C |                 | 8 SO        |

| MAX14840EATA+ | Symmetrical                                     | -40°C to +125°C | 8 TDFN-EP*  |

| MAX14841EASA+ | True                                            | -40°C to +125°C | 8 SO        |

| MAX14841EATA+ | True                                            | -40°C to +125°C | 8 TDFN-EP*  |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

<sup>\*</sup>EP = Exposed pad.

#### **ABSOLUTE MAXIMUM RATINGS**

| (Voltages referenced to GND.)                       |

|-----------------------------------------------------|

| VCC0.3V to +6.0V                                    |

| RE, RO0.3V to +(Vcc + 0.3V)                         |

| DE, DI0.3V to +6.0V                                 |

| A, B8.0V to +13.0V                                  |

| Short-Circuit Duration (RO, A, B) to GND Continuous |

| Continuous Power Dissipation (TA = +70°C)           |

| 8-Pin SO (derate 7.6mW/°C above +70°C) 606mW        |

| 8-Pin TDFN (derate 24.4mW/°C above +70°C) 1951mW    |

| Junction-to-Case Thermal Resistance (θJC) (Note 1)  |

| 8-Pin SO38°C/W                                      |

| 8-Pin TDFN8°C/W                                     |

| Junction-to-Ambient Thermal Resistance (θJA) | (Note 1)           |

|----------------------------------------------|--------------------|

| 8-Pin SO                                     | 132°C/W            |

| 8-Pin TDFN                                   | 41°C/W             |

| Operating Temperature Range                  | -40°C to $+125$ °C |

| Junction Temperature                         | +150°C             |

| Storage Temperature Range                    | -65°C to +150°C    |

| Lead Temperature (soldering, 10s)            | +300°C             |

| Soldering Temperature (reflow)               | +260°C             |

|                                              |                    |

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maxim-ic.com/thermal-tutorial">www.maxim-ic.com/thermal-tutorial</a>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### DC ELECTRICAL CHARACTERISTICS

$(VCC = +3.0V \text{ to } +3.6V, TA = -40^{\circ}C \text{ to } +125^{\circ}C, \text{ unless otherwise noted. Typical values are at } VCC = +3.3V \text{ and } TA = +25^{\circ}C.)$  (Notes 2, 3)

| PARAMETER                                             | SYMBOL           | CONDITIO                                                                                                                                                            | ONS                               | MIN  | TYP   | MAX  | UNITS |

|-------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------|-------|------|-------|

| POWER SUPPLY                                          |                  |                                                                                                                                                                     |                                   |      |       |      |       |

| Supply Voltage                                        | Vcc              |                                                                                                                                                                     |                                   | 3.0  |       | 3.6  | V     |

| Supply Current                                        | Icc              | $DE = \overline{RE} = V_{CC}, \text{ or}$ $DE = \overline{RE} = GND, \text{ or}$ $DE = V_{CC}, \overline{RE} = GND,$ $DI = V_{CC} \text{ or } GND, \text{ no load}$ |                                   |      | 1.5   | 4    | mA    |

| Shutdown Supply Current                               | Ish              | $DE = GND \text{ and } \overline{RE} = VC$                                                                                                                          | C                                 |      |       | 10   | μΑ    |

| DRIVER                                                |                  |                                                                                                                                                                     |                                   |      |       |      |       |

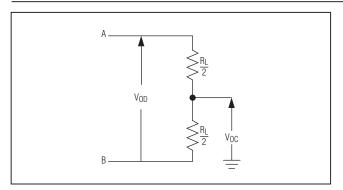

| Differential Driver Output                            | Vod              | $R_L = 54\Omega$ , Figure 1                                                                                                                                         |                                   | 1.5  |       |      | V     |

| Change in Magnitude of<br>Differential Output Voltage | ΔVOD             | $R_L = 54\Omega$ , Figure 1 (Note                                                                                                                                   | e 4)                              | -0.2 | 0     | +0.2 | V     |

| Driver Common-Mode Output<br>Voltage                  | Voc              | $R_L = 54\Omega$ , Figure 1                                                                                                                                         |                                   |      | Vcc/2 | 3    | V     |

| Change in Common-Mode<br>Voltage                      | ΔVoc             | $R_L = 54\Omega$ , Figure 1 (Note                                                                                                                                   | e 4)                              | -0.2 |       | 0.2  | V     |

| Single-Ended Driver Output High                       | Voн              | A/B output, IOUT = -20m                                                                                                                                             | A                                 | 2.2  |       |      | V     |

| Single-Ended Driver Output Low                        | Vol              | A/B output, I <sub>OUT</sub> = 20mA                                                                                                                                 |                                   |      |       | 0.8  | V     |

| Driver Short-Circuit Output                           | lloopl           | $0V \le V_{OUT} \le +12V$ , output low $-7V \le V_{OUT} \le V_{CC}$ , output high                                                                                   |                                   |      |       | 250  | mA    |

| Current                                               | llospl           |                                                                                                                                                                     |                                   | 250  |       |      | IIIA  |

| RECEIVER                                              |                  |                                                                                                                                                                     |                                   |      |       |      |       |

| Input Current (A and B)                               | I <sub>A,B</sub> | DE = GND,<br>VCC = GND or +3.6V                                                                                                                                     | $V_{IN} = +12V$<br>$V_{IN} = -7V$ | -800 |       | 1000 | μΑ    |

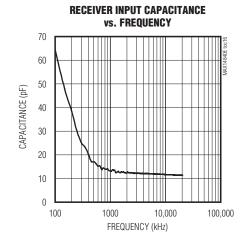

| Differential Input Capacitance                        | Са,в             | Between A and B, DE = GND, f = 2MHz                                                                                                                                 |                                   |      | 12    |      | pF    |

### **DC ELECTRICAL CHARACTERISTICS (continued)**

(VCC = +3.0V to +3.6V, TA = -40°C to +125°C, unless otherwise noted. Typical values are at VCC = +3.3V and TA = +25°C.) (Notes 2, 3)

| PARAMETER                                                   | SYMBOL          | CONDITIONS                                                               | MIN               | TYP  | MAX | UNITS |

|-------------------------------------------------------------|-----------------|--------------------------------------------------------------------------|-------------------|------|-----|-------|

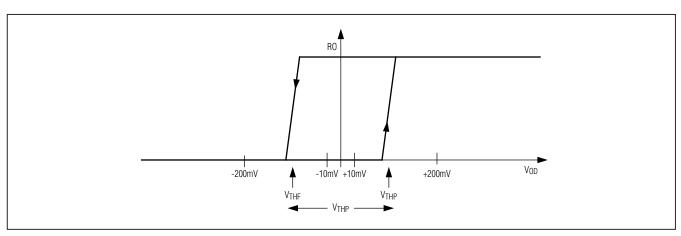

| Receiver Differential Threshold                             | VTHF            | -7V ≤ V <sub>CM</sub> ≤ 12V, V <sub>OD</sub> falling                     | -200              |      | -10 | mV    |

| Voltage (MAX14840E Only)                                    | VTHR            | $-7V \le V_{CM} \le 12V$ , $V_{OD}$ rising                               | 10                |      | 200 | mV    |

| Receiver Input Hysteresis (MAX14840E Only)                  |                 | VCM = 0V                                                                 | 20                | 170  |     | mV    |

| Receiver Differential Threshold<br>Voltage (MAX14841E Only) | VTH             | -7V ≤ V <sub>CM</sub> ≤ 12V                                              | -200              | -105 | -10 | mV    |

| Receiver Input Hysteresis<br>(MAX14841E Only)               | ΔVτΗ            | VCM = 0V                                                                 |                   | 10   |     | mV    |

| LOGIC INTERFACE                                             | '               |                                                                          |                   |      |     |       |

| loguet Ligh Voltage                                         | \/              | DE, DI                                                                   | 2.0               |      | 5.5 | V     |

| Input High Voltage                                          | VIH             | RE                                                                       | 2.0               |      |     | ] V   |

| Input Low Voltage                                           | VIL             | DE, DI, RE                                                               |                   |      | 0.8 | V     |

| Input Hysteresis                                            | VHYS            | DE, DI, RE                                                               |                   | 50   |     | mV    |

| Input Current                                               | I <sub>IN</sub> | DE, DI, RE                                                               | -1                |      | +1  | μΑ    |

| Input Impedance on First<br>Transition                      |                 | DE, RE                                                                   | 1                 |      | 10  | kΩ    |

| Output High Voltage                                         | Voн             | RE = GND, I <sub>O</sub> = -1mA, V <sub>A</sub> - V <sub>B</sub> > 200mV | V <sub>CC</sub> - |      |     | V     |

| Output Low Voltage                                          | VoL             | RE = GND, IO = 1mA, VA - VB < -200mV                                     |                   |      | 0.4 | V     |

| Three-State Output Current at Receiver                      | lozr            | RE = VCC, 0V ≤ VO ≤ VCC                                                  | -1                |      | +1  | μА    |

| Receiver Output Short-Circuit<br>Current                    | Iosr            | 0V ≤ V <sub>RO</sub> ≤ V <sub>CC</sub>                                   | -95               |      | +95 | mA    |

| PROTECTION                                                  | '               |                                                                          |                   |      |     |       |

| Thermal Shutdown Threshold                                  | T <sub>TS</sub> |                                                                          |                   | 160  |     | °C    |

| Thermal Shutdown Hysteresis                                 | TTSH            |                                                                          |                   | 15   |     | °C    |

|                                                             |                 | IEC 61000-4-2 Air Gap Discharge                                          |                   | ±20  |     |       |

| ESD Protection: A, B to GND                                 |                 | IEC 61000-4-2 Contact Discharge                                          | ±12               |      |     | kV    |

|                                                             |                 | HBM                                                                      |                   | ±35  |     |       |

| ESD Protection: All Other Pins                              |                 | HBM                                                                      |                   | ±2   |     | kV    |

### **SWITCHING CHARACTERISTICS**

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, T_A = -40 ^{\circ}\text{C} \text{ to } +125 ^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{CC} = +3.3 \text{V}$  and  $T_A = +25 ^{\circ}\text{C}$ .) (Notes 2, 3)

| PARAMETER                                    | SYMBOL   | CONDITIONS                                                     | MIN | TYP | MAX | UNITS |

|----------------------------------------------|----------|----------------------------------------------------------------|-----|-----|-----|-------|

| DRIVER                                       |          |                                                                |     |     |     |       |

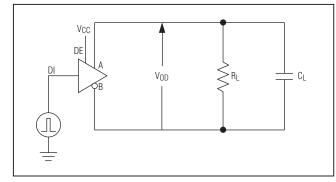

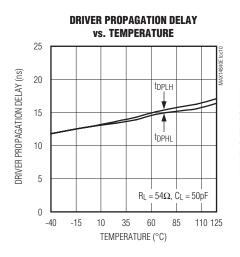

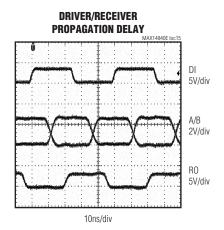

| Propagation Daloy                            | tDPLH    | $R_L = 54\Omega$ , $C_L = 50pF$ , Figures 2 and 3              | 5   | 12  | 20  | no    |

| Propagation Delay                            | tDPHL    | (Note 5)                                                       | 5   | 12  | 20  | ns    |

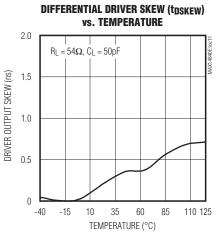

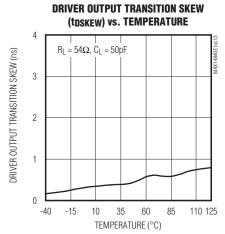

| Differential Driver Output Skew              | tdskew   | $R_L = 54\Omega$ , $C_L = 50pF$ , Figures 2 and 3 (Notes 5, 8) |     |     | 2   | ns    |

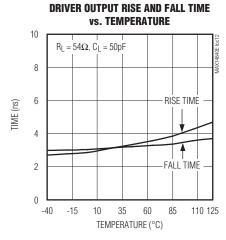

| Driver Differential Output Rise or Fall Time | tHL, tLH | $R_L = 54\Omega$ , $C_L = 50pF$ , Figures 2 and 3 (Notes 5, 8) |     |     | 7.5 | ns    |

### **SWITCHING CHARACTERISTICS (continued)**

$(VCC = +3.0V \text{ to } +3.6V, TA = -40^{\circ}\text{C to } +125^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } VCC = +3.3V \text{ and } TA = +25^{\circ}\text{C.})$  (Notes 2, 3)

| PARAMETER                                    | SYMBOL                 | CONDITIONS                                                      | MIN | TYP | MAX | UNITS |

|----------------------------------------------|------------------------|-----------------------------------------------------------------|-----|-----|-----|-------|

| Maximum Data Rate                            | DRMAX                  |                                                                 | 40  |     |     | Mbps  |

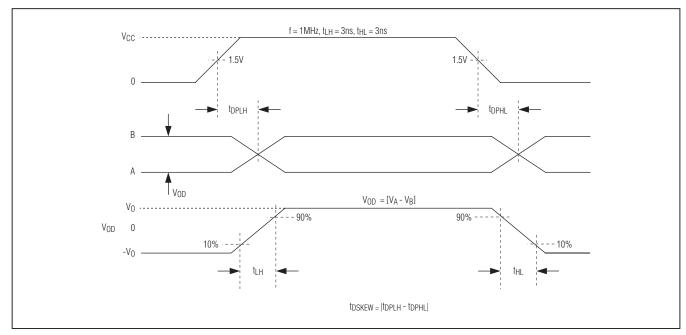

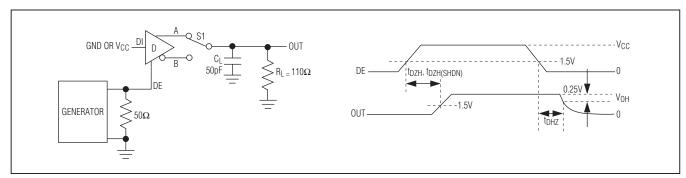

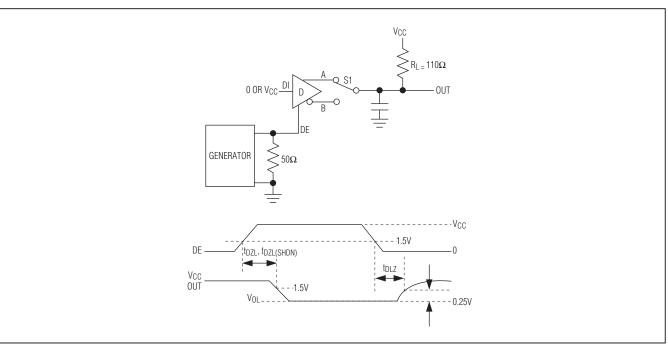

| Driver Enable to Output High                 | t <sub>DZH</sub>       | $R_L = 110\Omega$ , $C_L = 50$ pF, Figures 4 and 5 (Notes 5, 6) |     |     | 30  | ns    |

| Driver Enable to Output Low                  | tDZL                   | $R_L = 110\Omega$ , $C_L = 50$ pF, Figures 4 and 5 (Notes 5, 6) |     |     | 30  | ns    |

| Driver Disable Time from Low                 | tDLZ                   | $R_L = 110\Omega$ , $C_L = 50$ pF, Figures 4 and 5 (Notes 5, 6) |     |     | 30  | ns    |

| Driver Disable Time from High                | tDHZ                   | $R_L = 110\Omega$ , $C_L = 50pF$ , Figures 4 and 5 (Notes 5, 6) |     |     | 30  | ns    |

| Driver Enable from Shutdown to Output Low    | tDZL(SHDN)             | $R_L = 110\Omega$ , $C_L = 50$ pF, Figures 4 and 5 (Notes 5, 6) |     |     | 4   | μs    |

| Driver Enable from Shutdown to Output High   | tDZH(SHDN)             | $R_L = 110\Omega$ , $C_L = 50$ pF, Figures 4 and 5 (Notes 5, 6) |     |     | 4   | μs    |

| Time to Shutdown                             | tshdn                  | (Note 7)                                                        | 50  |     | 800 | ns    |

| RECEIVER                                     |                        |                                                                 |     |     |     |       |

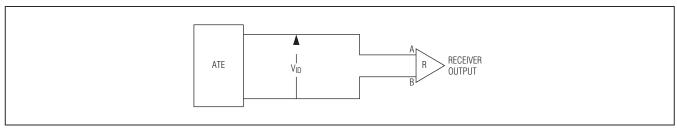

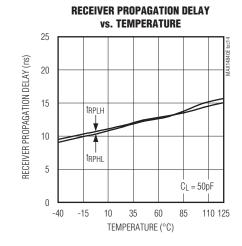

| Propagation Delay                            | trplh                  | trphe CL = 15pF, Figures 6 and 7 (Note 5)                       |     |     | 25  | ns    |

| Tropagation Delay                            | trphl                  |                                                                 |     |     | 25  | 115   |

| Receiver Output Skew                         | trskew                 | C <sub>L</sub> = 15pF, Figures 6 and 7 (Notes 5, 8)             |     |     | 2   | ns    |

| Maximum Data Rate                            | DRMAX                  |                                                                 | 40  |     |     | Mbps  |

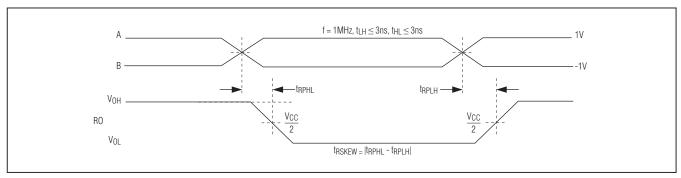

| Receiver Enable to Output High               | trzh                   | $R_L = 1k\Omega$ , $C_L = 15pF$ , Figure 8 (Notes 5, 6)         |     |     | 20  | ns    |

| Receiver Enable to Output Low                | tRZL                   | $R_L = 1k\Omega$ , $C_L = 15pF$ , Figure 8 (Notes 5, 6)         |     |     | 20  | ns    |

| Receiver Disable Time from Low               | tRLZ                   | $R_L = 1k\Omega$ , $C_L = 15pF$ , Figure 8 (Notes 5, 6)         |     |     | 20  | ns    |

| Receiver Disable Time from High              | trhz                   | $R_L = 1k\Omega$ , $C_L = 15pF$ , Figure 8 (Notes 5, 6)         |     |     | 20  | ns    |

| Receiver Enable from Shutdown to Output Low  | <sup>†</sup> RZL(SHDN) | $R_L = 1k\Omega$ , $C_L = 15pF$ , Figure 8 (Notes 5, 6)         |     |     | 4   | μs    |

| Receiver Enable from Shutdown to Output High | <sup>†</sup> RZH(SHDN) | $R_L = 1k\Omega$ , $C_L = 15pF$ , Figure 8 (Notes 5, 6)         |     |     | 4   | μs    |

| Time to Shutdown                             | tshdn                  | (Note 7)                                                        | 50  |     | 800 | ns    |

- Note 2: All devices are 100% production tested at  $T_A = +25^{\circ}C$ . Specifications for all temperature limits are guaranteed by design.

- **Note 3:** All currents into the device are positive; all currents out of the device are negative. All voltages are referenced to device ground, unless otherwise noted.

- Note 4: ΔVOD and ΔVOC are the changes in VOD and VOC, respectively, when the DI input changes state.

- Note 5: Capacitive load includes test probe and fixture capacitance.

- **Note 6:** The timing parameter refers to the driver or receiver enable delay when the device has exited the initial hot-swap protect state and is in normal operating mode.

- Note 7: Shutdown is enabled by driving  $\overline{\text{RE}}$  high and DE low. The device is guaranteed to have entered shutdown after tshon has elapsed.

- Note 8: Parameter is guaranteed by characterization and not production tested.

### **Test and Timing Diagrams**

Figure 1. Driver DC Test Load

Figure 2. Driver Timing Test Circuit

Figure 3. Driver Propagation Delays

Figure 4. Driver Enable and Disable Times (tDZH, tDHZ)

### **Test and Timing Diagrams (continued)**

Figure 5. Driver Enable and Disable Times (tDLZ, tDZL)

Figure 6. Receiver Propagation Delay Test Circuit

Figure 7. Receiver Propagation Delays

6 \_\_\_\_\_\_ /VI/XI/VI

## Test and Timing Diagrams (continued)

Figure 8. Receiver Enable and Disable Times

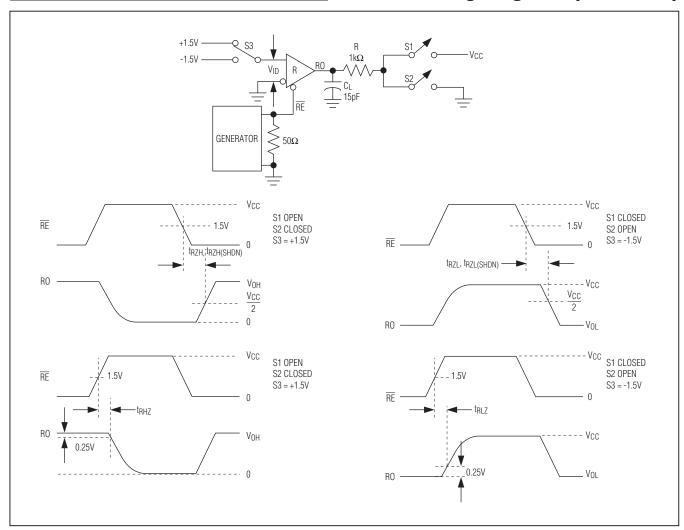

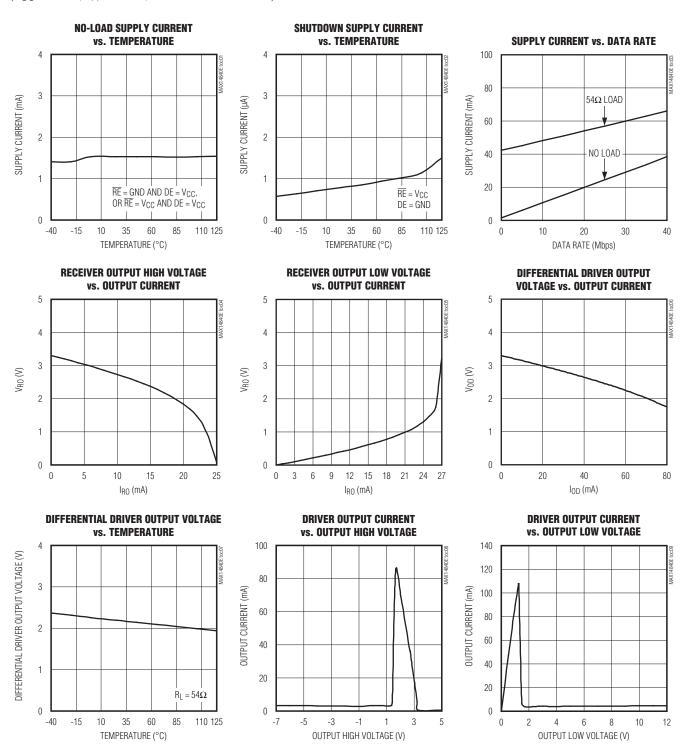

### **Typical Operating Characteristics**

(V<sub>CC</sub> = +3.3V, T<sub>A</sub> = +25°C, unless otherwise noted.)

### Typical Operating Characteristics (continued)

$(V_{CC} = +3.3V, T_A = +25^{\circ}C, unless otherwise noted.)$

### **Pin Configurations**

### **Pin Descriptions**

| PIN | NAME | FUNCTION                                                                                                                                                                                                                                                                                            |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | RO   | Receiver Output. See the Function Table.                                                                                                                                                                                                                                                            |

| 2   | RE   | Active-Low Receiver-Output Enable. Drive $\overline{RE}$ low to enable RO. RO is high impedance when $\overline{RE}$ is high. Drive $\overline{RE}$ high and DE low to enter low-power shutdown mode. $\overline{RE}$ is a hot-swap input (see the <i>Hot-Swap Capability</i> section for details). |

| 3   | DE   | Driver-Output Enable. Drive DE high to enable driver outputs. These outputs are high impedance when DE is low. Drive $\overline{\text{RE}}$ high and DE low to enter low-power shutdown mode. DE is a hot-swap input (see the <i>Hot-Swap Capability</i> section for details).                      |

| 4   | DI   | Driver Input. With DE high, a low on DI forces the A output low and the B output high. Similarly, a high on DI forces the A output high and the B output low.                                                                                                                                       |

| 5   | GND  | Ground                                                                                                                                                                                                                                                                                              |

| 6   | А    | Noninverting Receiver Input and Noninverting Driver Output                                                                                                                                                                                                                                          |

| 7   | В    | Inverting Receiver Input and Inverting Driver Output                                                                                                                                                                                                                                                |

| 8   | Vcc  | Positive Supply Voltage Input. Bypass VCC with a 0.1µF ceramic capacitor to GND.                                                                                                                                                                                                                    |

| _   | EP   | Exposed Pad (TDFN Only). Connect EP to GND.                                                                                                                                                                                                                                                         |

### **Function Table**

|    |        | TRANSMITTING         |                     |                     |  |  |

|----|--------|----------------------|---------------------|---------------------|--|--|

|    | INPUTS |                      | OUTF                | PUTS                |  |  |

| RE | DE     | DI                   | В                   | А                   |  |  |

| Χ  | 1      | 1                    | 0                   | 1                   |  |  |

| Χ  | 1      | 0                    | 1                   | 0                   |  |  |

| 0  | 0      | X                    | High Impedance      | High Impedance      |  |  |

| 1  | 0      | X                    | Shutdown            | (see note)          |  |  |

|    |        | RECEIVING (MAX14840E | <br>≣)              |                     |  |  |

|    | INPUTS |                      | OUTF                | PUTS                |  |  |

| RE | DE     | A-B                  | R                   | 0                   |  |  |

| 0  | X      | ≥ 200mV              | 1                   |                     |  |  |

| 0  | X      | ≤ -200mV             | 0                   |                     |  |  |

| 0  | X      | Open/Shorted         | Previous State      |                     |  |  |

| 1  | 1      | X                    | High Imp            | pedance             |  |  |

| 1  | 0      | X                    | Shutdown            | Shutdown (see note) |  |  |

|    |        | RECEIVING (MAX14841E | ≣)                  |                     |  |  |

|    | INPUTS | ·                    | OUTF                | PUTS                |  |  |

| RE | DE     | A-B                  | RO                  |                     |  |  |

| 0  | X      | ≥ -10mV              | 1                   |                     |  |  |

| 0  | X      | ≤ -200mV             | 0                   |                     |  |  |

| 0  | X      | Open/Shorted         | 1                   |                     |  |  |

| 1  | 1      | X                    | High Imp            | High Impedance      |  |  |

| 1  | 0      | X                    | Shutdown (see note) |                     |  |  |

X = Don't care.

Note: Shutdown mode, driver, and receiver outputs are in high impedance.

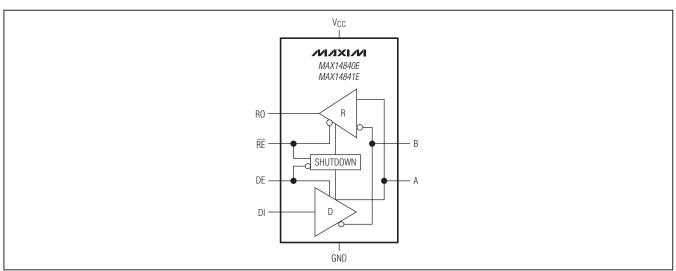

### **Functional Diagram**

### **Detailed Description**

The MAX14840E/MAX14841E are +3.3V ESD-protected RS-485 transceivers intended for high-speed, half-duplex communications. A hot-swap capability eliminates false transitions on the bus during power-up or hot insertion.

The MAX14840E features symmetrical fail-safe and larger receiver hysteresis, providing improved noise rejection and improved recovered signals in high-speed and long cable applications. The MAX14841E has true fail-safe receiver inputs guaranteeing a logic-high receiver output when inputs are shorted or open. All devices have a 1-unit load receiver input impedance, allowing up to 32 transceivers on the bus.

The MAX14840E/MAX14841E transceivers draw 1.5mA (typ) supply current when unloaded or when fully loaded with the drivers disabled.

#### Symmetrical Fail Safe (MAX14840E)

At high data rates and with long cable lengths, the signal at the end of the cable is attenuated and distorted due to the lowpass characteristic of the transmission line. Under these conditions, fail-safe RS-485 receivers, which have offset threshold voltages, produce recovered signals with uneven mark-space ratios. The MAX14840E has symmetrical receiver thresholds, as shown in Figure 9. This produces near even mark-space ratios at the receiver's output (RO). The MAX14840E also has higher receiver hysteresis than the MAX14841E and most other RS-485 transceivers. This results in higher receiver noise tolerance.

Symmetrical fail safe means that the receiver's output (RO) remains at the same logic state that it was before the differential input voltage VoD went to 0V. Under

normal conditions, where UART signaling is used, this means that the state on the line prior to all drivers being disabled is a logic-high (i.e., a UART STOP bit).

#### True Fail Safe (MAX14841E)

The MAX14841E guarantees a logic-high receiver output when the receiver inputs are shorted or open or when they are connected to a terminated transmission line with all drivers disabled. This is the case if the receiver input threshold is between -10mV and -200mV. RO is logic-high if the differential receiver input voltage VoD is greater than or equal to -10mV.

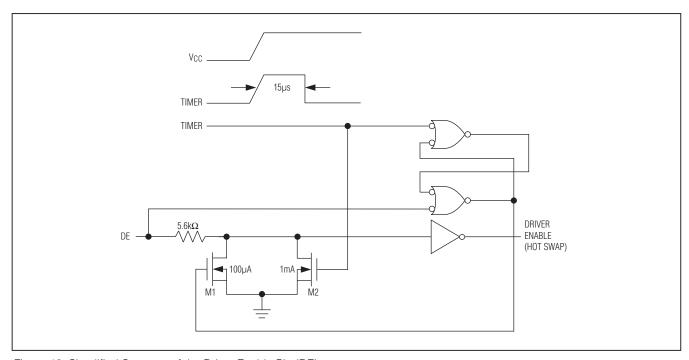

## **Hot-Swap Capability**Hot-Swap Inputs

When circuit boards are inserted into a hot or powered backplane, disturbances to the enable inputs and differential receiver inputs can lead to data errors. Upon initial circuit board insertion, the processor undergoes its power-up sequence. During this period, the processor output drivers are high impedance and are unable to drive the DE and  $\overline{\rm RE}$  inputs of the MAX14840E/MAX14841E to a defined logic level. Leakage currents up to 10µA from the high-impedance output of a controller could cause DE and  $\overline{\rm RE}$  to drift to an incorrect logic state. Additionally, parasitic circuit board capacitance could cause coupling of VCC or GND to DE and  $\overline{\rm RE}$ . These factors could improperly enable the driver or receiver. However, the MAX14840E/MAX14841E have hot-swap inputs that avoid these potential problems.

When  $V_{CC}$  rises, an internal pulldown circuit holds DE low and  $\overline{RE}$  high. After the initial power-up sequence, the pulldown circuit becomes transparent, resetting the hot-swap-tolerable inputs.

Figure 9. Symmetrical Hysteresis

#### How-Swap Input Circuitry

The MAX14840E/MAX14841E DE and RE enable inputs feature hot-swap capability. At the input, there are two nMOS devices, M1 and M2 (Figure 10). When VCC ramps from OV, an internal 15µs timer turns on M2 and sets the SR latch that also turns on M1. Transistors M2 (a 1mA current sink) and M1 (a 100uA current sink) pull DE to GND through a  $5.6k\Omega$  resistor. M2 is designed to pull DE to the disabled state against an external parasitic capacitance up to 100pF that can drive DE high. After 15µs, the timer deactivates M2 while M1 remains on, holding DE low against three-state leakages that can drive DE high. M1 remains on until an external source overcomes the required input current. At this time, the SR latch resets and M1 turns off. When M1 turns off, DE reverts to a standard, high-impedance CMOS input. Whenever VCC drops below 1V, the hot-swap input is

For  $\overline{RE}$ , there is a complementary circuit employing two pMOS devices pulling  $\overline{RE}$  to VCC.

#### ±35kV ESD Protection

ESD protection structures are incorporated on all pins to protect against electrostatic discharges encountered during handling and assembly. The driver outputs and receiver inputs of the MAX14840E family of devices have extra protection against static electricity. The ESD structures withstand high ESD in all states: normal operation, shutdown, and powered down. After an ESD event, the MAX14840E/MAX14841E keep working without latchup or damage.

ESD protection can be tested in various ways. The transmitter outputs and receiver inputs of the MAX14840E/MAX14841E are characterized for protection to the following limits:

- ±35kV HBM

- ±20kV using the Air Gap Discharge method specified in IEC 61000-4-2

- ±12kV using the Contact Discharge method specified in IEC 61000-4-2

Figure 10. Simplified Structure of the Driver Enable Pin (DE)

#### **ESD Test Conditions**

ESD performance depends on a variety of conditions. Contact Maxim for a reliability report that documents test setup, test methodology, and test results.

#### **Human Body Model**

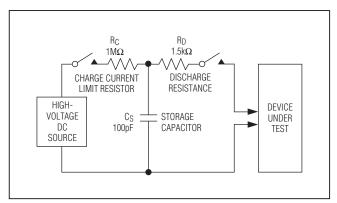

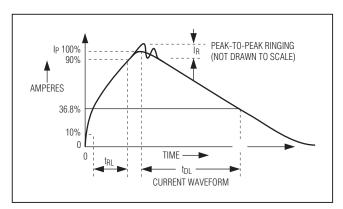

Figure 11 shows the HBM, and Figure 12 shows the current waveform it generates when discharged into a low-impedance state. This model consists of a 100pF capacitor charged to the ESD voltage of interest, which is then discharged into the test device through a  $1.5 \mathrm{k}\Omega$  resistor.

#### IEC 61000-4-2

The IEC 61000-4-2 standard covers ESD testing and performance of finished equipment. However, it does not specifically refer to integrated circuits. The MAX14840E/MAX14841E family of devices helps you design equipment to meet IEC 61000-4-2, without the need for additional ESD protection components.

Figure 11. Human Body ESD Test Model

Figure 12. Human Body current Waveform

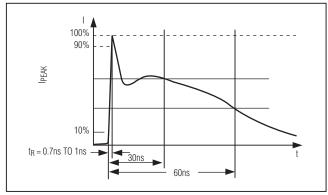

The major difference between tests done using the HBM and IEC 61000-4-2 is higher peak current in IEC 61000-4-2 because series resistance is lower in the IEC 61000-4-2 model. Hence, the ESD withstand voltage measured to IEC 61000-4-2 is generally lower than that measured using the HBM.

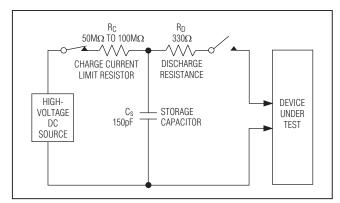

Figure 13 shows the IEC 61000-4-2 model, and Figure 14 shows the current waveform for IEC 61000-4-2 ESD Contact Discharge test.

### Applications Information

#### **High-Speed Operation**

The MAX14840E and MAX14841E are high-performance RS-485 transceivers supporting data rates up to 40Mbps.

#### **Driver Output Protection**

Two mechanisms prevent excessive output current and power dissipation caused by faults or by bus contention. Current limit on the output stage provides

Figure 13. IEC 61000-4-2 ESD Test Model

Figure 14. IEC 61000-4-2 ESD Generator Current Waveform

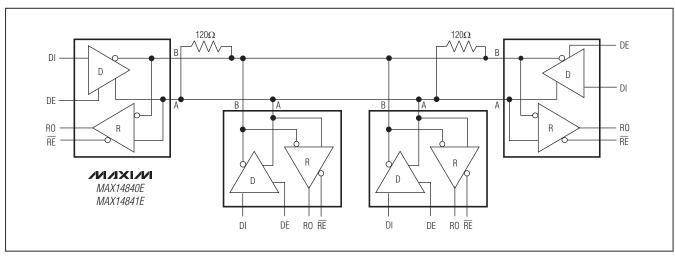

Figure 15. Typical Half-Duplex RS-485 Network

immediate protection against short circuits over the whole common-mode voltage range (see the *Typical Operating Characteristics*). Additionally, a thermal shutdown circuit forces the driver outputs into a high-impedance state if the die temperature exceeds +160°C (typ).

#### **Low-Power Shutdown Mode**

Low-power shutdown mode is initiated by bringing  $\overline{RE}$  high and DE low. In shutdown, the devices draw less than 10 $\mu$ A of supply current.

RE and DE can be driven simultaneously; the parts are guaranteed not to enter shutdown if RE is high and DE is low for less than 50ns. If the inputs are in this state for at least 800ns, the parts are guaranteed to enter shutdown.

#### **Typical Applications**

The MAX14840E/MAX14841E transceivers are designed for bidirectional data communications on multipoint bus transmission lines. Figure 15 shows a typical network application circuit. To minimize reflections, terminate the line at both ends with its characteristic impedance and keep stub lengths off the main line as short as possible.

\_Chip Information

PROCESS: BICMOS

### Package Information

For the latest package outline information and land patterns, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |

|--------------|--------------|----------------|

| 8 SO         | S8+4         | 21-0041        |

| 8 TDFN-EP    | T833+2       | <u>21-0137</u> |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.